模擬集成電路設計流程 版圖驗證的重要性

在模擬集成電路(IC)的設計流程中,版圖驗證是不可或缺的關鍵步驟,直接決定了芯片的最終性能和可靠性。它位于物理設計階段之后、芯片制造之前,主要目的是確保版圖設計滿足電氣性能、制造工藝和可靠性等要求。版圖驗證通常包括幾個核心組成部分:設計規則檢查(DRC)、電學規則檢查(ERC)、版圖與電路圖一致性檢查(LVS)以及寄生參數提取。

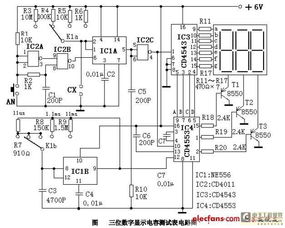

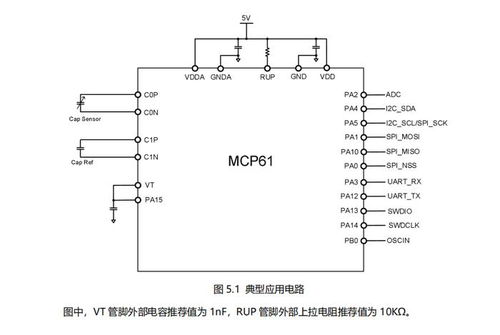

設計規則檢查(DRC)用于驗證版圖是否符合代工廠的制造工藝規范,例如最小線寬、間距、覆蓋層等。這一步確保芯片在生產過程中不會因物理尺寸問題導致缺陷。

電學規則檢查(ERC)關注版圖中的電氣連接問題,如短路、開路或懸浮節點,避免功能故障。

然后,版圖與電路圖一致性檢查(LVS)將版圖與原始電路圖進行對比,確保兩者在功能和連接上完全匹配。如果存在不一致,工程師必須修改版圖以糾正錯誤。

寄生參數提取用于分析版圖中引入的寄生電阻、電容和電感,這些參數可能影響電路的頻率響應、功耗和信號完整性。提取結果通常反饋到電路仿真中,以優化設計。

通過嚴格的版圖驗證,可以顯著降低芯片制造失敗的風險,提高成品率,并確保集成電路在真實應用中穩定運行。隨著工藝節點不斷縮小,版圖驗證的復雜性日益增加,需要借助自動化工具和專業知識來高效完成。版圖驗證是模擬集成電路設計流程中的守護者,保障著從設計到制造的順利過渡。

如若轉載,請注明出處:http://www.tdjszp.com.cn/product/32.html

更新時間:2026-01-08 07:09:25