在平面與網(wǎng)頁設(shè)計的廣闊領(lǐng)域中,抽象線條設(shè)計與矢量素材正日益成為塑造獨特視覺語言與空間感的核心元素。它們超越了具象形態(tài)的束縛,通過純粹的點、線、面、色彩與形態(tài),構(gòu)建出深邃、流動且充滿想象力的視覺空間。

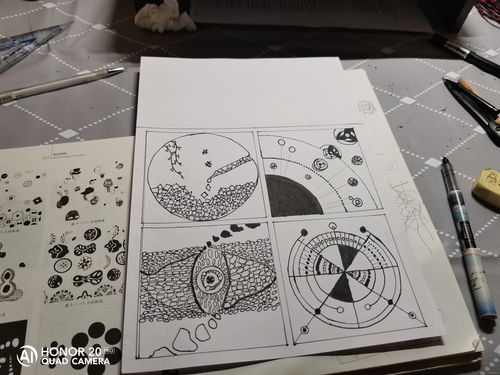

空間感,在設(shè)計中并非指代真實的三維物理空間,而是一種通過視覺元素營造出的深度、層次與動勢的感知。抽象線條在其中扮演了至關(guān)重要的角色。一條流暢的曲線,可以引導(dǎo)觀者的視線在畫面中蜿蜒前行,創(chuàng)造出動態(tài)的路徑與節(jié)奏;一組交織的直線,則可能構(gòu)建出穩(wěn)固的框架或富有張力的網(wǎng)格,暗示著結(jié)構(gòu)與秩序。這些線條本身是二維的,但通過粗細(xì)、疏密、方向與曲直的變化,它們能在平面上暗示出前后、遠(yuǎn)近、虛實的關(guān)系,從而在觀者心中喚起立體的空間聯(lián)想。

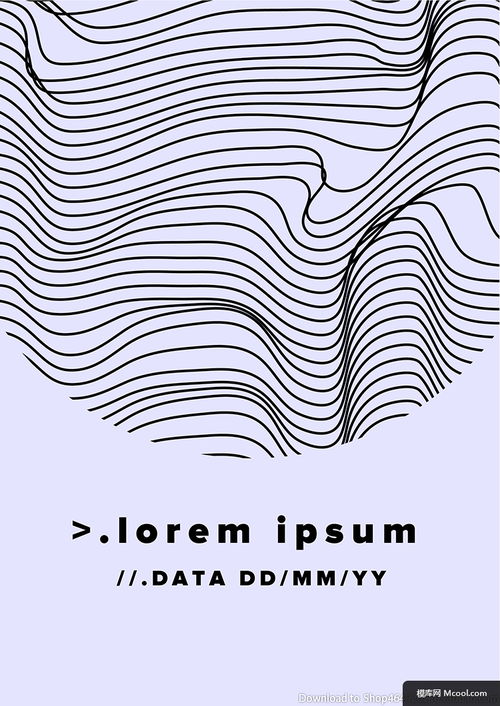

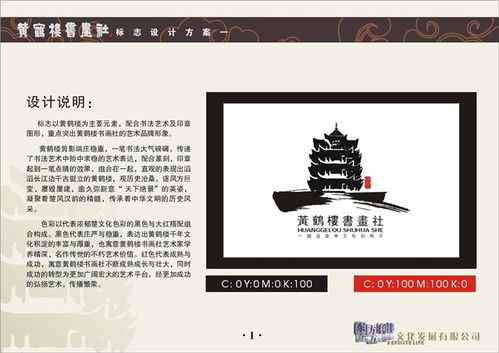

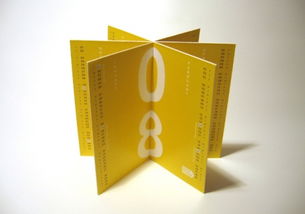

矢量素材,以其無限縮放不失真、編輯靈活的特性,成為實現(xiàn)此類抽象線條設(shè)計的理想載體。設(shè)計師可以自由地創(chuàng)造、組合與變形幾何圖形與貝塞爾曲線,生成從簡約到繁復(fù)、從理性到感性的各種抽象形態(tài)。無論是模擬自然流動的有機(jī)線條,還是體現(xiàn)科技感的精密幾何網(wǎng)絡(luò),矢量格式都能確保其清晰、銳利與可塑性。在平面設(shè)計(如海報、品牌視覺、包裝)中,抽象線條矢量圖常作為背景紋理、視覺焦點或裝飾元素,為靜態(tài)畫面注入活力與深度,提升設(shè)計的藝術(shù)性與現(xiàn)代感。

當(dāng)設(shè)計場域轉(zhuǎn)移到網(wǎng)頁與交互界面時,抽象線條與矢量素材的應(yīng)用被賦予了更多的功能性與動態(tài)可能。在網(wǎng)頁設(shè)計中,它們不僅是美化視覺的裝飾:

- 引導(dǎo)與導(dǎo)航:線條可以巧妙地連接不同的內(nèi)容區(qū)塊,引導(dǎo)用戶視線流,或作為視覺線索指示交互點(如按鈕、鏈接)。

- 劃分與組織空間:抽象的線框或色塊能夠在不使用生硬分割線的情況下,清晰地區(qū)分網(wǎng)頁的不同功能區(qū)域,保持界面的通透與整體感。

- 創(chuàng)造動態(tài)與背景:通過CSS或JavaScript動畫,靜態(tài)的矢量線條可以轉(zhuǎn)化為流動的背景、加載動畫或微交互效果,極大地增強(qiáng)用戶體驗的趣味性與沉浸感。平滑的矢量動畫能營造出一種無縫、流暢的空間過渡感。

- 響應(yīng)式設(shè)計的適應(yīng)性:矢量圖形(如SVG格式)能完美適應(yīng)不同屏幕尺寸與分辨率,確保抽象線條構(gòu)成的視覺空間感在各種設(shè)備上都能保持一致性與高品質(zhì)。

將“空間感、曲線、矢量素材、抽象線條”這些關(guān)鍵詞融合,指向的是一種現(xiàn)代的設(shè)計哲學(xué):用最精簡、最富有表現(xiàn)力的視覺元素,構(gòu)建出意蘊豐富的數(shù)字或印刷空間。它要求設(shè)計師不僅關(guān)注形式的美感,更要理解線條的“引力”與“節(jié)奏”,以及它們?nèi)绾闻c空白(負(fù)空間)互動,共同定義出一個平衡、和諧且引人探索的視覺場域。

抽象線條與矢量素材是連接平面設(shè)計與網(wǎng)頁設(shè)計的橋梁,是構(gòu)建當(dāng)代視覺空間感的強(qiáng)大工具。它們以無形的律動駕馭有形的界面,將理性的信息架構(gòu)與感性的藝術(shù)表達(dá)融為一體,持續(xù)為觀者與用戶帶來新穎、深邃且高效的視覺體驗。