在高端住宅市場,樣板間不僅是銷售工具,更是品牌理念與生活方式的集中展示。其中,新古典風格的別墅樣板間,以其典雅、奢華與永恒的魅力,備受青睞。本文將圍繞一套編號為19070472的精品別墅施工圖設計資源,探討新古典風格在工裝設計與施工中的關鍵要點,并提供相關CAD圖紙資源的獲取與應用思路。

一、 新古典風格的精髓與樣板間定位

新古典主義風格源于對古希臘、羅馬古典藝術的復興與簡化,它摒棄了巴洛克與洛可可時期的過度裝飾,追求對稱、秩序與理性的美感。在別墅樣板間設計中,這一風格通常體現為:

- 宏偉的對稱結構:平面布局講求中軸線與對稱性,營造莊重、穩定的空間感。

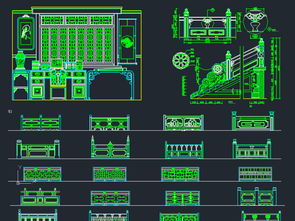

- 經典的裝飾元素:運用簡化的羅馬柱、山花、線板、拱券等建筑符號,以及浮雕、金屬鑲嵌等精致細節。

- 高雅和諧的色調:常以米白、金色、深棕、墨綠等為主色調,搭配大理石、絲絨、實木等材質,彰顯奢華質感。

- 現代功能的融合:在古典形制中,無縫融入現代生活所需的智能化系統、開放式空間布局及舒適性設施。

一套編號如19070472的精品施工圖,其價值在于精準地將上述風格理念轉化為可執行的施工藍圖,確保從空間規劃到裝飾細節的精準落地。

二、 施工圖設計:品質別墅的建造基石

對于“工裝”(商業空間裝修,此處指樣板間)而言,施工圖是溝通設計、施工與材料采購的核心文件。一套完整的別墅樣板間施工圖集(CAD圖紙)通常包含:

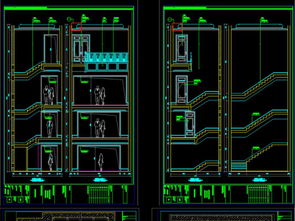

- 平面圖系列:包括原始結構圖、平面布置圖、地面鋪裝圖、天花布置圖、燈具定位圖、開關插座點位圖等。這些圖紙定義了空間的功能分區、動線流線及所有固定設施的精確位置。

- 立面圖與剖面圖:詳細展示墻面造型、護墻板、門窗套、定制柜體及背景墻的設計,標注材質、尺寸和工藝做法,是新古典裝飾細節得以呈現的關鍵。

- 節點大樣圖:針對復雜的裝飾線條、收口、吊頂、樓梯等部位進行放大詳圖設計,確保施工精度和工藝品質。

- 水電暖通等專業圖紙:確保隱蔽工程的安全、合規與高效,并服務于智能家居等現代舒適系統。

編號19070472這樣的資源,為設計師、開發商及施工方提供了一個高品質的參考模板,可以極大地提升設計起點和施工標準化水平。

三、 資源獲取與應用:CAD圖紙大全與網頁設計啟示

“工裝施工CAD圖紙圖片大全”類資源平臺,匯集了大量如19070472的實戰案例。在獲取和應用這類資源時,應注意:

- 版權與合規使用:確保資源來源合法,尊重原創設計。此類圖紙主要用于學習參考、方案靈感啟發或內部技術研究,直接用于商業項目需謹慎處理版權或進行深度二次創作。

- 深化設計與本地化:任何現成圖紙都需根據項目實際的地質條件、建筑面積、法規要求及客戶具體需求進行深化、調整和優化。

- 跨專業協同:施工圖是建筑、室內、結構、設備等多專業協同作業的成果,應用時需考慮各專業圖紙的匹配與整合。

承載這些資源的“網頁設計”本身也提供了用戶體驗啟示。一個優秀的圖紙資源網站,應具備清晰的分類(如按風格、戶型、空間)、精準的搜索(如通過編號19070472直接定位)、高質量的預覽圖以及規范的文件下載格式,這本身也是“設計”服務于“功能”的體現。

###

從一張編號為19070472的新古典風格別墅施工圖出發,我們看到的不僅是一套圖紙,更是一條貫穿設計理念、施工工藝與最終品質呈現的完整鏈條。對于從業者而言,善用這類精品資源庫,結合深入的風格理解與扎實的本地化設計,是打造出真正打動人心的高檔品質別墅樣板間的有效途徑。在追求高效的牢記設計的初心與版權的底線,方能實現創意與價值的雙贏。